# RTAX-DSP Radiation-Tolerant FPGAs

## **Projected Radiation Performance**

- SEU-Hardened Registers Eliminate the Need for Triple-Module Redundancy (TMR)

- Immune to Single-Event Upsets (SEU) to LET<sub>TH</sub> > 37 MeV-cm<sup>2</sup>/mg

- SEU Rate < 10<sup>-10</sup> Errors/Bit-Day in Worst-Case Geosynchronous Orbit

- Expected SRAM Upset Rate of <10<sup>-10</sup> Errors/Bit-Day with Use of Error Detection and Correction (EDAC) IP (included) with Integrated SRAM Scrubber

- Single-Bit Correction, Double-Bit Detection

- Variable-Rate Background Refreshing

- Total Ionizing Dose Up to 300 krad (Si, Functional)

- Single-Event Latch-Up Immunity (SEL) to LET<sub>TH</sub> > 117MeV-cm<sup>2</sup>/mg

- TM1019 Test Data Available

## **Embedded Multiply/Accumulate Blocks**

- Up to 120 Multiply/Accumulate Blocks

- Fully SEU- and SET-Hardened

- 125 MHz Performance throughout Military Temperature

- Flexible, Cascadable Accumulate Function

## Processing Flows

- B-Flow MIL-STD-883B

- E-Flow Actel Extended Flow

- EV-Flow Class V Equivalent Flow Processing

## **Prototyping Options**

RTAX-DSP PROTO Devices with Same Functional and Timing Characteristics as Flight Unit in a Non-Hermetic Package

## **Leading-Edge Performance**

- High-Performance Embedded FIFOs

- 350+ MHz System Performance

- 500+ MHz Internal Performance

- 700 Mbps LVDS Capable I/Os

## **Specifications**

- Up to 4 Million Equivalent System Gates or 500 k Equivalent ASIC Gates

- Up to 16,800 SEU-Hardened Flip-Flops

- Up to 840 I/Os

- Up to 540 kbits Embedded SRAM

- Manufactured on Advanced 0.15 µm CMOS Antifuse Process Technology, 7 Layers of Metal

### **Features**

- Single-Chip, Nonvolatile Solution 1.5 V Core Voltage for Low Power

- Flexible, Multi-Standard I/Os:

- 1.5 V, 1.8 V, 2.5 V, 3.3 V Mixed Voltage Operation Bank-Selectable I/Os 8 Banks per Chip Single-Ended I/O Standards: LVTTL, LVCMOS, 3.3 V PCI

- JTAG Boundary Scan Testing (as per IEEE 1149.1) Differential I/O Standards: LVPECL and LVDS

- Voltage-Referenced I/O Standards: GTL+, Class 1, SSTL2 Class 1 and 2, SSTL3 Class 1 and 2

- Hot-Swap Compliant with Cold-Sparing Support (Except PCI)

- Embedded Memory with Variable Aspect Ratio and Organizations:

- Independent, Width-Configurable Read and Write **Ports**

- Programmable Embedded FIFO Control Logic

- **ROM Emulation Capability**

- Deterministic, User-Controllable Timing

- Unique In-System Diagnostic and Debug Capability

Table 1 • **RTAX-DSP Family Product Profile**

| Device                                | RTAX2000D | RTAX4000D |

|---------------------------------------|-----------|-----------|

| Capacity                              |           |           |

| Equivalent System Gates               | 2,000,000 | 4,000,000 |

| ASIC Gates                            | 250,000   | 500,000   |

| Modules                               |           |           |

| Register (R-cells)                    | 9,856     | 18,480    |

| Combinatorial (C-cells)               | 19,712    | 36,960    |

| Flip-Flops (maximum)                  | 19,712    | 36,960    |

| Embedded Multiply / Accumulate Blocks |           |           |

| DSP Mathblocks                        | 64        | 120       |

| Embedded RAM/FIFO (without EDAC)      |           |           |

| Core RAM Blocks                       | 64        | 120       |

| Core RAM Bits $(k = 1,024)$           | 288 k     | 540 k     |

| Clocks (segmentable)                  |           |           |

| Hardwired                             | 4         | 4         |

| Routed                                | 4         | 4         |

| I/Os                                  |           |           |

| I/O Banks                             | 8         | 8         |

| User I/Os (maximum)                   | 684       | 840       |

| I/O Registers                         | 2,052     | 2,520     |

| Package                               |           |           |

| CCGA/LGA (DSP)                        | 1272      | 1272      |

| COFP                                  | 352       | 352       |

**Note:** The body size of the 1272-pin CCGA and LGA packages used on the RTAX-DSP devices is slightly larger than the body size of the 1272-pin CCGA and LGA used on the RTAX4000S/SL devices.

© 2009 Actel Corporation

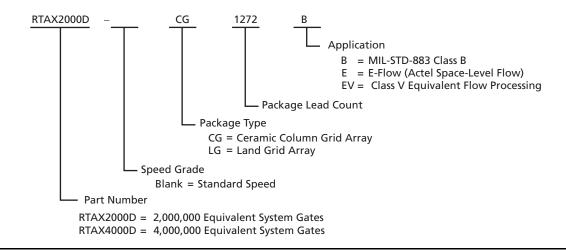

# **Ordering Information**

# **Temperature Grade Offerings**

| Package       | RTAX2000D | RTAX4000D |

|---------------|-----------|-----------|

| CQ352         | B, E, EV  | B, E, EV  |

| CG1272/LG1272 | B, E, EV  | B, E, EV  |

Note: \*The 1272-pin Ceramic Column Grid Array (CCGA) packages with Six Sigma columns.

B = MIL-STD-883 Class B

E = E-Flow (Actel Space-Level Flow) EV = Actel "V" Equivalent Flow

# **Speed Grade and Temperature Grade Matrix**

|    | Std. |

|----|------|

| В  | ✓    |

| Е  | ✓    |

| EV | V    |

Contact your local Actel representative for device availability.

### **Device Resources**

|               | User I/Os (including clock buffers) |           |

|---------------|-------------------------------------|-----------|

| Device        | RTAX2000D                           | RTAX4000D |

| CQ352         | TBD                                 | 150       |

| CG1272/LG1272 | 684                                 | 840       |

**Note:** CCGA = Ceramic Column Grid Array, LGA = Land Grid Array

# **Actel MIL-STD-883 Class B Product Flow**

Table 2 ● Actel MIL-STD-883 Class B Product Flow for RTAX-DSP\*

| Step | Screen                                                                                    | Method                                                                                                                                       | Requirement |

|------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1    | Internal Visual                                                                           | 2010, Condition B                                                                                                                            | 100%        |

| 2    | Serialization                                                                             |                                                                                                                                              | 100%        |

| 3    | Temperature Cycling                                                                       | 1010, Condition C, 10 cycles minimum                                                                                                         | 100%        |

| 4    | Constant Acceleration                                                                     | 2001, Y1 Orientation Only<br>Condition TBD                                                                                                   | 100%        |

| 5    | Particle Impact Noise Detection                                                           | 2020, Condition A                                                                                                                            | 100%        |

| 6    | Seal (Fine & Gross Leak Test)                                                             | 1014                                                                                                                                         | 100%        |

| 7    | Pre-Burn-In Electrical Parameters                                                         | In accordance with applicable Actel device specification                                                                                     | 100%        |

| 8    | Dynamic Burn-In                                                                           | 1015, Condition D,<br>160 hours at 125°C or 80 hours at 150°C minimum                                                                        | 100%        |

| 9    | Interim (Post-Burn-In) Electrical Parameters                                              | In accordance with applicable Actel device specification                                                                                     | 100%        |

| 10   | Percent Defective Allowable (PDA) Calculation                                             | 5%                                                                                                                                           | All Lots    |

| 11   | Final Electrical Test  a. Static Tests (1) 25°C (2) -55°C and +125°C  b. Functional Tests | In accordance with applicable Actel device specification, which includes a, b, and c: 5005, Table 1, Subgroup 1 5005, Table 1, Subgroup 2, 3 | 100%        |

|      | (1) 25°C<br>(2) –55°C and +125°C<br>c. Switching Tests at 25°C                            | 5005, Table 1, Subgroup 7<br>5005, Table 1, Subgroup 8a, 8b<br>5005, Table 1, Subgroup 9                                                     |             |

| 12   | External Visual                                                                           | 2009                                                                                                                                         | 100%        |

**Note:** \*For CCGA devices, all Assembly, Screening, and TCl testing is performed at LGA level. Only QA electrical and mechanical visual tests are performed after solder column attachment.

## **Actel Extended Flow**

Table 3 ◆ Actel Extended Flow for RTAX-DSP<sup>1, 2, 3</sup>

| Step | Screen                                                                           | Method                                                                                                                                       | Requirement        |

|------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 1    | Destructive Bond Pull <sup>4</sup>                                               | 2011, Condition D                                                                                                                            | Extended<br>Sample |

| 2    | Internal Visual                                                                  | 2010, Condition A                                                                                                                            | 100%               |

| 3    | Serialization                                                                    |                                                                                                                                              | 100%               |

| 4    | Temperature Cycling                                                              | 1010, Condition C, 10 cycles minimum                                                                                                         | 100%               |

| 5    | Constant Acceleration                                                            | 2001, Y1 Orientation Only<br>Condition TBD                                                                                                   |                    |

| 6    | Particle Impact Noise Detection                                                  | 2020, Condition A                                                                                                                            | 100%               |

| 7    | Radiographic (X-Ray)                                                             | 2012, One View (Y1 Orientation) Only                                                                                                         | 100%               |

| 8    | Pre-Burn-In Electrical Parameters                                                | In accordance with applicable Actel device specification                                                                                     |                    |

| 9    | Dynamic Burn-In                                                                  | 1015, Condition D,<br>240 hours at 125°C or 120 hours at 150°C minimum                                                                       | 100%               |

| 10   | Interim (Post-Dynamic-Burn-In) Electrical Parameters                             | In accordance with applicable Actel device specification                                                                                     | 100%               |

| 11   | Static Burn-In                                                                   | 1015, Condition C, 72 hours at 150°C or 144 hours at 125°C minimum                                                                           | 100%               |

| 12   | Interim (Post-Static-Burn-In) Electrical Parameters                              | In accordance with applicable Actel device specification                                                                                     | 100%               |

| 13   | Percent Defective Allowable (PDA) Calculation                                    | 5% Overall, 3% Functional Parameters at 25°C                                                                                                 | All Lots           |

| 14   | Final Electrical Test <sup>4</sup> a. Static Tests (1) 25°C (2) -55°C and +125°C | In accordance with applicable Actel device specification, which includes a, b, and c: 5005, Table 1, Subgroup 1 5005, Table 1, Subgroup 2, 3 | 100%               |

|      | b. Functional Tests (1) 25°C (2) -55°C and +125°C c. Switching Tests at 25°C     | 5005, Table 1, Subgroup 7<br>5005, Table 1, Subgroup 8a, 8b<br>5005, Table 1, Subgroup 9                                                     |                    |

| 15   | Seal (Fine & Gross Leak Test)                                                    | 1014                                                                                                                                         | 100%               |

| 16   | External Visual                                                                  | 2009                                                                                                                                         | 100%               |

#### Notes:

- 1. Actel offers Extended Flow for users requiring additional screening beyond MIL-STD-833, Class B requirement. Extended Flow incorporates the majority of the screening procedures as outlined in Method 5004 of MIL-STD-883, Class S.

- 2. The Quality Conformance Inspection (QCI) for Extended Flow devices still complies to the MIL-STD-833, Class B requirement.

- 3. For CCGA devices, all Assembly/Screening/TCI testing is performed at LGA level. Only QA electrical and mechanical visual tests are performed after solder column attachment.

- 4. Requirement for 100% nondestructive bond pull per Method 2003 is substituted by an extensive destructive bond pull to Method 2011 Condition D on an extended sample basis.

# **Actel "EV" Flow (Class V Flow Equivalent Processing)**

Table 4 • Actel "EV" Flow (Class V Equivalent Flow Processing) for RTAX-DSP<sup>1, 2</sup>

| Step | Screen                                                                              | Method                                                                                                                                       | Requirement     |

|------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1    | Destructive Bond Pull <sup>3</sup>                                                  | 2011, Condition D                                                                                                                            | Extended Sample |

| 2    | Internal Visual                                                                     | 2010, Condition A                                                                                                                            | 100%            |

| 3    | Serialization                                                                       |                                                                                                                                              | 100%            |

| 4    | Temperature Cycling                                                                 | 1010, Condition C, 50 cycles minimum                                                                                                         | 100%            |

| 5    | Constant Acceleration                                                               | 2001, Y1 Orientation Only<br>Condition TBD                                                                                                   | 100%            |

| 6    | Particle Impact Noise Detection                                                     | 2020, Condition A                                                                                                                            | 100%            |

| 7    | Radiographic (X-Ray)                                                                | 2012, One View (Y1 Orientation) Only                                                                                                         | 100%            |

| 8    | Pre-Burn-In Electrical Parameters                                                   | In accordance with applicable Actel device specification                                                                                     | 100%            |

| 9    | Dynamic Burn-In                                                                     | 1015, Condition D,<br>240 hours at 125°C or 120 hours at 150°C<br>minimum                                                                    |                 |

| 10   | Interim (Post-Dynamic-Burn-In) Electrical Parameters                                | In accordance with applicable Actel device specification                                                                                     | 100%            |

| 11   | Static Burn-In                                                                      | 1015, Condition C, 72 hours at 150°C or 144 hours at 125°C minimum                                                                           | 100%            |

| 12   | Interim (Post-Static-Burn-In) Electrical Parameters                                 | In accordance with applicable Actel device specification                                                                                     | 100%            |

| 13   | Percent Defective Allowable (PDA) Calculation                                       | 5% Overall, 3% Functional Parameters at 25°C                                                                                                 | All Lots        |

| 14   | Final Electrical Test <sup>3, 4</sup> a. Static Tests (1) 25°C (2) –55°C and +125°C | In accordance with applicable Actel device specification, which includes a, b, and c: 5005, Table 1, Subgroup 1 5005, Table 1, Subgroup 2, 3 | 100%            |

|      | b. Functional Tests (1) 25°C (2) –55°C and +125°C                                   | 5005, Table 1, Subgroup 7<br>5005, Table 1, Subgroup 8a, 8b                                                                                  |                 |

|      | c. Switching Tests at 25°C                                                          | 5005, Table 1, Subgroup 9                                                                                                                    |                 |

| 15   | Seal (Fine & Gross Leak Test)                                                       | 1014                                                                                                                                         | 100%            |

| 16   | External Visual                                                                     | 2009                                                                                                                                         | 100%            |

| 17   | Wafer Lot Specific Life Test (Group C)                                              | MIL-PRF-38535, Appendix B, sec. B.4.2.c                                                                                                      | All Wafer Lots  |

### Notes:

- 1. Actel offers "EV" flow for users requiring full compliance to the MIL-PRF-38535 Class V requirement.

The "EV" process flow is expanded from the existing E-flow requirement (it still meets the full SMD requirement for current E-flow devices) with the intention to be in full compliance to the MIL-PRF-38535 Table IA and Appendix B requirement, but without the official Class V certification from DSCC.

- 2. For CCGA devices, all Assembly/Screening/TCI testing is performed at LGA level. Only QA electrical and mechanical visual tests are performed after solder column attachment.

- 3. The requirement for 100% nondestructive bond pull per Method 2003 is fulfilled by substitution of an extensive extended sample basis.

- 4. Read and record performed at −55°C and +125°C (no delta calculation).

# **General Description**

# RTAX-DSP Mathblock Functional Description

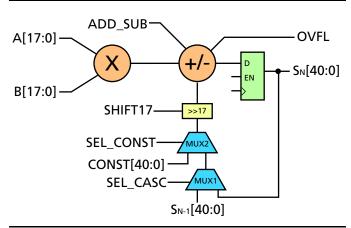

The flexible elements of the RTAX-DSP Mathblocks enable easy integration into many different signal processing topologies, such as Fast Fourier Transforms, Inverse Fast Fourier Transforms, Finite Impulse Response Filters, Infinite Impulse Response Filters, and Discrete Cosine Transforms. The hardwired Mathblocks also enable acceleration of high precision single- and double-floating point multiplications. Figure 1-1 shows a basic functional diagram of a Mathblock.

Figure 1-1 • RTAX-DSP Mathblock

The Mathblocks comprise the following elements:

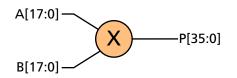

### 1. Multiplier

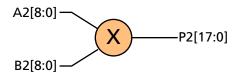

The multiplier operates on two signed 18-bit factors, A[17:0] and B[17:0] (Figure 1-2). The multiplier produces a signed 36-bit output, which is provided as an input to the add/subtract function. The output of the multiplier can optionally bypass the add/subtract function.

Figure 1-2 • RTAX-DSP Mathblock Multiplier Configured as Signed 18x18

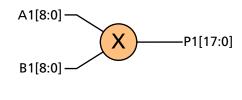

The multiplier can be fractured to implement two instances of signed 9x9 multiplication (Figure 1-3).

Figure 1-3 • Mathblock Configured with Two Independent Signed 9x9 multipliers

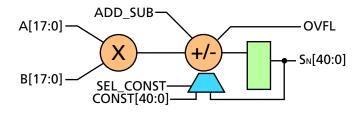

- 2. Adder/Subtractor plus MUX Control

- The adder/subtractor can perform the following functions:

- Accumulate using feedback.

- Create higher precision multipliers using the S<sub>N-1</sub> input and the 17-bit shift function.

- Create complex DSP functions, such as FIR filters, by cascading Mathblocks together using the S<sub>N-1</sub> input.

- The initial value of the accumulate function can be set using the value defined on the CONST bus.

Overflow or underflow of the add/subtract function is indicated by the OVFL output.

Figure 1-4 shows the Mathblock configured to perform multiply and accumulate functions. FPGA resources can be used to extend the accumulate width.

Figure 1-4 • Mathblock Configured to Perform Multiply and Accumulate Functions

### 3. Output Register

The output of the adder/subtractor block is presented to a 41-bit output register. The register has a clock input, an enable input, a set or reset input, and provides a 41-bit output  $S_N[40:0]$  to the exterior of the Mathblock. Signals  $S_N[40:0]$  are also fed back within the Mathblock to the accumulator multiplexer stack to enable various accumulation functions.

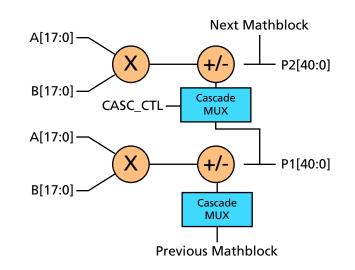

### 4. Cascading Mathblocks

Mathblocks may be cascaded together to form complex DSP structures such as FIR filters and FFTs. Figure 1-5 shows the configuration of Mathblocks cascaded together.

Figure 1-5 • Mathblocks Cascaded Together as Part of a Complex DSP Function

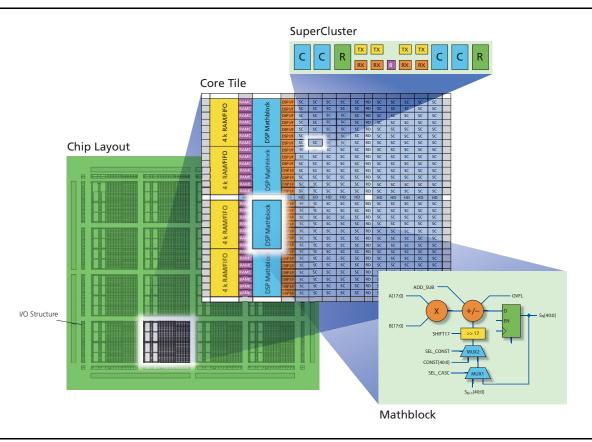

# **RTAX-DSP Architecture**

The overall RTAX-DSP device architecture is shown in Figure 1-6. In each core tile, there are four Mathblocks, which are located adjacent to the SRAM/FIFO blocks. The Mathblocks are evenly distributed across the device, to help achieve uniform performance of DSP functions.

Figure 1-6 • RTAX-DSP Device Architecture Overview

# **Datasheet Categories**

### **Categories**

In order to provide the latest information to designers, some datasheets are published before data has been fully characterized. Datasheets are designated as "Product Brief," "Advance," and "Production". The definition of these categories are as follows:

### **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

#### Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

## **Unmarked (production)**

This version contains information that is considered to be final.

# **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Actel Safety Critical, Life Support, and High-Reliability Applications Policy

The Actel products described in this advance status document may not have completed Actel's qualification process. Actel may amend or enhance products during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any Actel product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult Actel's Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of Actel's products is available on the Actel website at http://www.actel.com/documents/ORT\_Report.pdf. Actel also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local Actel sales office for additional reliability information.

Actel and the Actel logo are registered trademarks of Actel Corporation.

All other trademarks are the property of their owners.

Actel is the leader in low-power and mixed-signal FPGAs and offers the most comprehensive portfolio of system and power management solutions. Power Matters. Learn more at www.actel.com.

### **Actel Corporation**

2061 Stierlin Court Mountain View, CA 94043-4655 USA

**Phone** 650.318.4200 **Fax** 650.318.4600

### Actel Europe Ltd.

River Court, Meadows Business Park Station Approach, Blackwater Camberley Surrey GU17 9AB United Kingdom

**Phone** +44 (0) 1276 609 300 **Fax** +44 (0) 1276 607 540

### **Actel Japan**

EXOS Ebisu Building 4F 1-24-14 Ebisu Shibuya-ku Tokyo 150 Japan

**Phone** +81.03.3445.7671 **Fax** +81.03.3445.7668 www.jp.actel.com

### **Actel Hong Kong**

Room 2107, China Resources Building 26 Harbour Road Wanchai, Hong Kong **Phone** +852 2185 6460

**Phone** +852 2185 6460 **Fax** +852 2185 6488 www.actel.com.cn